Technology for Package

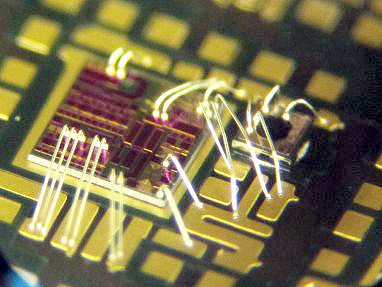

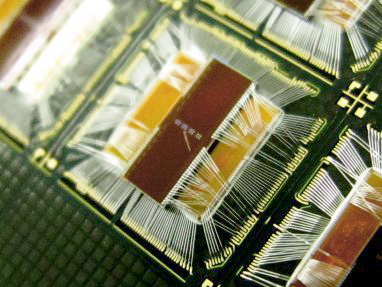

Cu/Ag Wire

Wire bonding은 얇은 wire를 이용해 전기적인 신호를 연결하는 기술입니다. 열과 압력, ultrasonic energy를 이용해 얇은 wire를 용융(熔融) 상태로 만들어 pad에 접합시키는 방법입니다.

오랫동안 wire 재료로 사용되었던 금(Au)은 가격이 비싸고 계속 가격이 상승하므로, 상대적으로 가격이 낮은 구리(Cu)를 wire 재료로 이용하는 개발이 진행 중입니다. Amkor에서는 Cu wire 공정개발을 10년 전부터 진행했으며, 다양한 package 경험과 0.6~2.0mil까지 검증된 기술이 있습니다. 특히 Lead Frame과 Laminate 제품에 Cu wire bonding 기술을 적용해 대량 양산하기도 합니다. 2006년부터 전 세계 Amkor Factory에서 Cu wire 기술을 이용한 대량 양산을 진행하는 등, 전 세계 Amkor Factory 내에 Cu wire BOM/BKMs가 확립되어 있습니다.

Ag wire의 작업성과 yield, UPH가 Au wire와 같은 수준입니다. Wire bonding 기술 중에서 SSB(die to die)에 적용할 때 Cu wire보다 더 나은 performance를 가지고 있습니다. FAB의 hardness가 Cu wire보다는 낮으므로(PCC 기준) pad damage가 Au wire와 같은 수준을 지니고, PCC보다 넓은 공정 parameter range와 낮은 Al splash를 가집니다. 2015년 6월 기준으로, 8곳의 customer와 23개의 device에 적용되어 대량 양산하고 있습니다. 0.8mil 이하부터 AgHP는 PCC wire보다 가격이 저렴하다는 특징을 지닙니다.

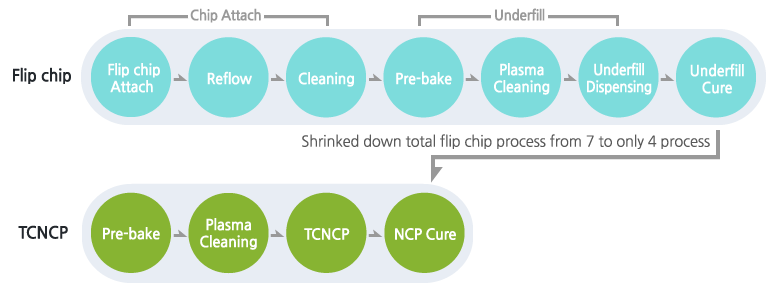

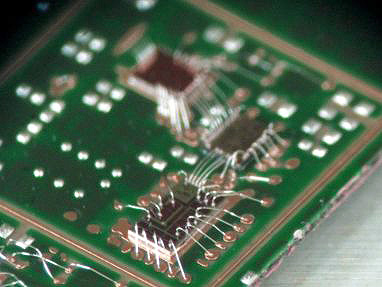

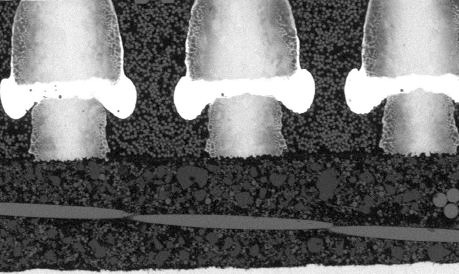

TCNCP

앰코는 기존 flip chip process와 다른 새로운 공정을 적용한 flip chip package를 제공합니다. TCNCP 공정은 Thermal Compression Non Conductive Paste의 약자로, 비전도성 용액을 활용해 열압착 공정을 통한 advanced interconnection 기술을 제공합니다. TCNCP 공정은 수 가지의 프로세스를 하나의 프로세스로 구현할 수 있는 특징이 있습니다. Chip attach를 위해 기본적으로 필요한 Reflow / Flux Cleaning / Underfill 공정이 통합된 프로세스로 제공되며, 각각의 장비에 필요한 공간 배치와 자원을 획기적으로 줄일 수 있다는 장점을 가집니다. TCNCP 공정은 기존 솔더범프의 사이즈나 구조의 한계점을 극복할 수 있는 Cu pillar 범프를 적용해 양산에 성공했으며, 이를 통해 Fine Pitch(< 80㎛)를 구현했습니다. 특히, 미세피치(Fine Pitch)를 통한 범프 디자인의 용이성과 더불어 chip 사이즈 축소 등 다양한 활용으로 기술을 발전시키고 서비스를 폭넓게 제공합니다.

- Transceivers

- Embedded Processors

- Application Processors

- Power Management, Baseband

- ASICs and SOCs

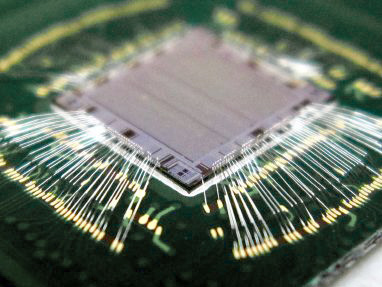

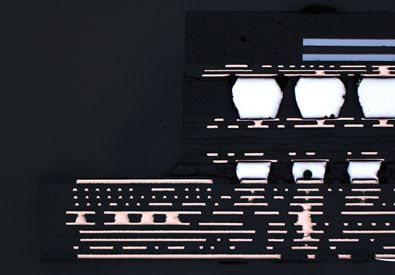

Substrate

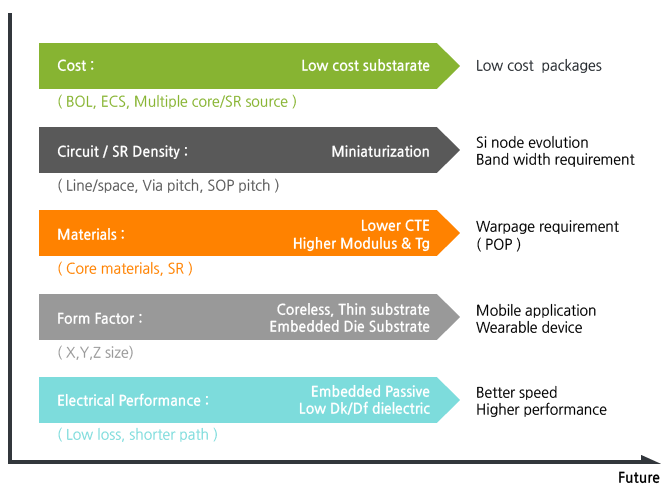

패키지용 substrate는 IC 반도체 chip과 PWB(Printed Wiring Board) 보드 기판 간 전기적/기계적/열적 연결하는 기판으로, 반도체 패키지의 구성요소 중 하나입니다. PCB나 PWB와 같은 일반 기판은 데스크톱 PC나 mobile 기기 등에서 흔히 보는 메인보드 기판을 말하는 것이며, 반도체 패키지용에 사용되는 기판은 이보다 고밀도/고집적화된 디자인을 가지는 기판입니다. 그래서 substrate라고 명시해 일반 PCB와 구별합니다. 최근 반도체 미세공정의 급속적인 발전과 지속적인 패키지의 경박단소화 요구에 맞추어, substrate 기술개발 또한 가속하는 중입니다. 더욱이 최근에는 mobile, wearable, 사물 인터넷 등 마켓에서의 고성능 못지않게 저가형 제품 trend의 시장요구에 맞춰 초저가형 substrate의 기술개발도 필요하게 되었습니다. 현재 Amkor에서는 이러한 Market trend와 고객의 요구에 대응하기 위해 substrate 관련 연구개발을 지속해서 진행 중입니다.

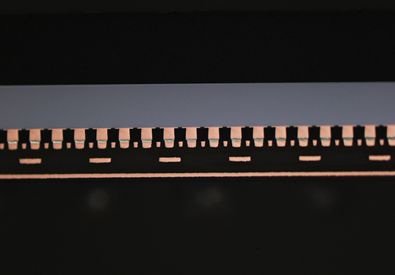

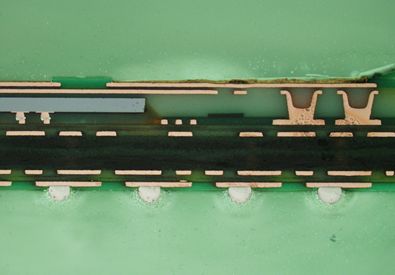

일반적으로 반도체 패키지에서 substrate의 cost는 전체 패키지 가격에서 많은 비중을 차지합니다. 이에 따라 가격경쟁력을 갖추기 위해 substrate의 가격을 줄이는 것이 무엇보다 효과적인 solution입니다. 대표적인 예로, 기존 SOP(solder on pad) type의 substrate에서는 IC 반도체 chip과 substrate 간 전기적 연결을 위해 substrate에 솔더범프라는 조건을 갖추고 반도체 chip의 범프와 접합을 통해 패키징했습니다. 그러나 substrate 제조가격이나 수율, 생산성 측면에서 SOP 공정이 상당한 부분을 차지하기에 SOP를 배제하는 기술개발이 이루어졌고, 현재는 non SOP type의 substrate들이 저가형 substrate로서 큰 역할을 합니다. 더욱이 substrate에서 솔더범프가 없어진 대신, 최외층 범프패드나 회로패턴 위에 바로 chip의 범프와 연결하는 기술이 동시에 개발되었고, BOL(Bump on Lead), BOT(Bump on Trace), BOP(Bump on Pad) 등의 chip 실장방식이 그러한 기술들이며, 이러한 구조는 SOP type의 substrate보다 더욱 미세회로 및 미세범프피치를 구현할 수 있다는 성능적 장점이 있습니다.

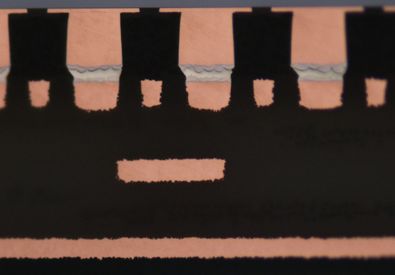

반도체 실리콘 미세공정의 급속적인 발전과 함께, 갈수록 고성능의 패키지들이 요구됩니다. Substrate 또한 그것에 맞게 기술개발이 이루어지는 중입니다. 또한, 고성능과 더불어 전자기기 장치의 슬림화 요구로 패키지의 form factor는 점진적으로 줄어들고 있기에, substrate의 form factor 역시 줄어들어야 하는 실정입니다. 고성능/슬림화의 대표적인 예로, EPS(Embedded Passive in Substrate) 기술과 EDS(Embedded Die in Substrate) 기술이 있습니다. EPS/EDS는 수동소자 또는 능동소자를 substrate 내에 실장함으로써 패키지 슬림화에 적합하며, 전기적 신호연결경로가 단축되어 성능 또한 우수해진다는 장점이 있습니다. 또한, 초고성능 고밀도 substrate 구현을 위해 최근에는 기존 substrate 미세 패터닝 공법이 아닌 반도체 wafer level 패터닝 공법을 활용해, 미세선폭(L/S, Line and Space)을 3㎛ 수준까지 구현하는 substrate 기술개발이 진행 중입니다. 이는 기존의 장치, 재료, 공정을 활용한 wet 공법이 아닌 반도체용 노광장치, 재료, 공정을 활용한 dry 공법을 substrate 제조공정에 맞게 적용하고 구현하는 것입니다. Substrate 슬림화 역시 기본적으로 기존 cored type의 substrate에서 coreless type의 substrate로 변화하면서 슬림화와 성능적인 유리함이 있으며, 고밀도/고집적화 substrate 기술이 발전함에 따라 substrate의 layer count(층수, 層數)를 줄여가며 슬림화에 대응합니다.

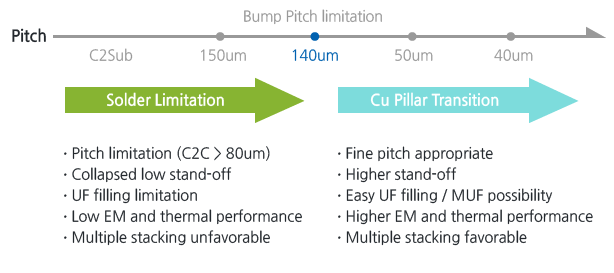

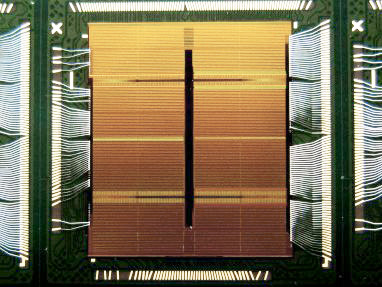

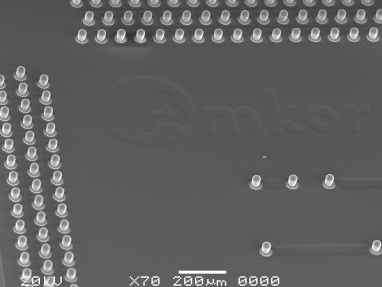

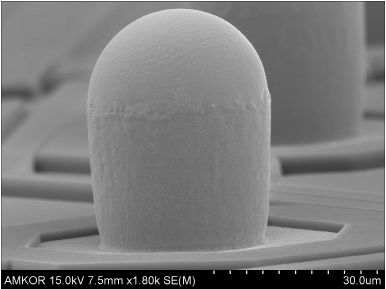

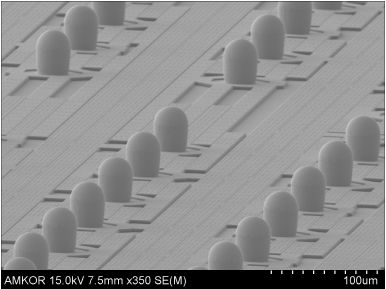

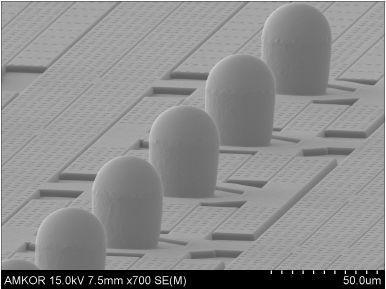

Cu pillar

반도체 chip의 패키지 기술은 경박단소/고성능/고효율이라는 큰 틀을 가지고 발전해 왔습니다. 이러한 trend에 맞추어 Amkor 역시 앰코만의 다양한 기술들을 개발해 왔고, 특히 flip chip 관련 기술은 이러한 특성을 잘 반영한 패키지입니다. 이 flip chip을 구현하기 위해서는 다양한 bumping 기술이 필요한데, 그중 Cu pillar 범핑은 flip chip을 구현하는 데 있어서 경박단소/고성능/고효율을 가능하게 하는 아주 중요한 기술입니다. 최근의 반도체 chip은 하나의 chip이 다양한 기능을 수행하고 처리속도도 점점 빨라지는 동시에, 필연적으로 입출력단자 수가 증가하고 pitch는 점점 작아지는 추세입니다. 이러한 상황을 flip chip 패키지로 구현하려면 기존의 솔더범프(Solder Bump)로는 한계가 있고, Cu pillar라는 범프가 필요하게 되었습니다. 이미 Cu pillar는 다양한 패키지에 이용되고 있고 앞으로 그 활용도는 더욱 높아질 전망입니다. 앰코의 Cu pillar 기술은 업계최고수준이며 앞으로도 고객의 요구에 부응하는 기술개발로 새로운 부가가치를 창출하는 핵심기술로 자리매김할 것입니다.

- 50㎛ 이하의 미세피치(Fine Pitch)를 구현할 수 있다.

- Substrate의 층수를 줄여 원가를 절감할 수 있다.

- Electromigration 특성이 뛰어나 대전류용(high current carrying capacity application) 소자에 이용할 수 있다.

- Low-k 디바이스에 이용할 수 있다.

- TSV(Through Silicon Via), CoC(Chip On Chip)와 같은 40㎛ 이하 초미세피치/최첨단 패키지에 이용할 수 있다.

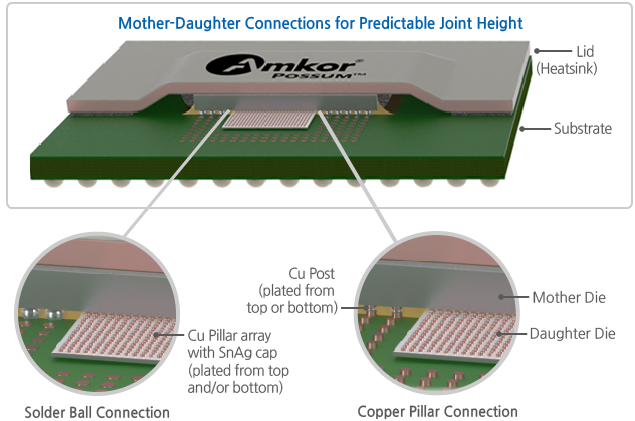

POSSUM

- Leverage fine pitch CuP bumping and die stacking capabilities in production

- Broaden package applications and space

Applications

- MEMS, automotive, mobile, networking, power management, optoelectronics

- Formats : CSP, PBGA, WLCSP, FCBGA, FusionQuad®

Value proposition

- Package size and form factor reduction

- Performance improvements

: Lower power dissipation

: Higher density

: Faster systems

MEMS/Sensor

- MEMS 구조가 받는 stress의 조절이 가능해야 합니다.

- MEMS 구조에 외부신호가 손실 없이 전달되어야 합니다.

- MEMS와 ASIC 소자를 외부 충격으로부터 보호해야 합니다.

Automotive Market

- 높은 수준의 신뢰성이 필요합니다.

- MEMS sensor 종류에 따른 맞춤 사양이 필요합니다.

Consumer Market

- 빠른 개발 시간이 필요합니다.

- 재활용이 가능한 PKG의 특성을 보입니다.

- MEMS PKG의 소형화가 지속해서 이루어져야 합니다.