Emerging PKG & Technology

TSV

TSV wafer에 대한 Amkor에서의 주요 공정들

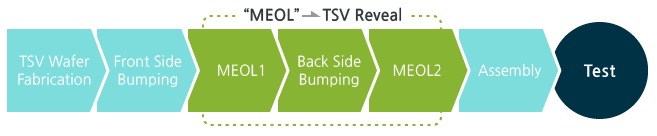

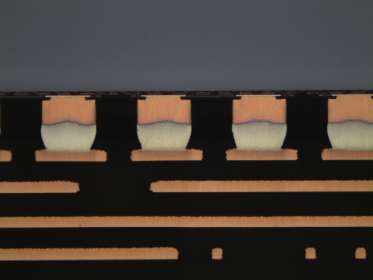

TSV(관통전극) 기술은 가장 낮은 에너지에서의 매우 높은 성능과 기능의 요구에 대해 2.5D와 3D 패키징 애플리케이션 및 아키텍처의 넓은 범위를 제공하기 위해 등장했습니다. 이러한 2.5D/3D 아키텍처에서 TSV 사용을 가능케 하고 TSV wafer의 대량 가공을 위해 Amkor에서는 많은 패키징 기술 플랫폼을 개발해 왔습니다. Amkor의 wafer 프로세스는 TSV가 이미 형성된 300mm wafer로부터 시작합니다. Amkor의 wafer 공정은 wafer를 얇게 가공하고 TSV 상호연결을 위해 뒷면 범핑단자를 만들고 최종적으로 다이를 적층하는 기술들을 확보하고 있습니다.

- Wafer support bonding and de-bonding

- TSV wafer thinning

- TSV reveal and CMP

- Back side passivation

- Redistribution as required

- Lead-free plating of micro-pillar and C4 interconnects

- Flip chip stacking for micro-pillar and C4 bump

- Wafer-level probe and Assembly unit test for TSV products

TSV Wafer Processing Flow

RtMLF

RtMLF (Routable Molded Lead Frame)

모바일 전자제품의 고성능화에 필요한 다양한 응용기술들이 집적화 및 다기능화되고 있습니다. 단순한 통화기능에서 컴퓨터와 같이 연산하고 명령을 수행하는 범위를 뛰어넘어, 이제는 센서 및 연결성(connectivity)의 핵심제품으로 성장하며 경쟁이 가속화되고 있습니다. 이와 같은 변화의 시기에 고객과 시장의 요구사항을 충족시키기 위해, 기존 제품에서 장단점을 보완하는 제품간 합종연횡이 활발히 연구 중입니다. 수십 년 동안 반도체 제품의 주류였던 Lead Frame 제품은 뛰어난 열적 특성에도 I/O 숫자의 제한과 수십 나노 단위의 반도체 공정기술의 발전을 따라가지 못해 PCB Laminate 제품으로 고성능 제품의 기능을 넘겨줘야 했습니다. 그러나 PCB Laminate 제품이 가지고 있는 상대적 저신뢰성 및 가격경쟁력은 또 다른 도전이 되는 실정이며, 고집적에 따른 열적 성능저하에 대한 우려도 증가하는 중입니다. 최근 모바일 제품에 사용한 패키지 제품을 분석하더라도 경박단소화와 가격경쟁력, 그리고 성능향상을 위한 패키지 변화를 쉽게 확인할 수 있습니다.

즉, 모바일 제품은 더는 브랜드별 가치와 차이를 구분할 수 없을 정도로 범용화되고 있으며 이러한 패러다임의 전환기에 무엇보다 중요한 것이 가격경쟁력과 차별화된 요소의 도입이라 하겠습니다. 이에 Lead Frame의 우수한 열적/전기적 특성을 유지하면서 많은 I/O 수를 수용할 수 있는 구조, 그리고 PCB Laminate의 팬인(Fan-in) 및 팬아웃(Fan-out) 설계유연성을 유지하면서 가격경쟁력을 향상시킬 수 있는 구조의 패키지가 필요하게 되었습니다. 이는 wafer level에서 진행되는 WLFO(Wafer Level Fan-out)의 molded 구조와 유사하며, 상호경쟁이나 보완의 구조로 판단됩니다. 이러한 시장의 요구사항을 바탕으로, Lead Frame과 Laminate 제품의 장점이 있는 혼합형 구조인 RtMLF(Routable Molded Lead Frame) 패키지를 개발했습니다.

Lead Frame과 Laminate 제품이 지닌 각각의 한계를 극복하고 장점을 살리는 새로운 1층의 몰딩 기판(molded substrate)인 RtMLF(Routable Molded Lead Frame)는 Lead Frame이 가지고 있는 우수한 열적 특성을 유지하기 위해 E-PAD 구조를 형성할 수 있고, 상층에 전기적 간섭을 최소화하기 위한 half-etching(Puddle) 구조도 형성할 수 있습니다. 또한, Laminate 제품이 가진 신호집적도를 구현할 수 있으며, 열적/전기적 시뮬레이션을 통해 우수성이 검증되었습니다. RtMLF는 여러 응용분야에서 적용이 가능할 것으로 판단되며, 시장의 요구사항에 맞게 다양한 제품군에 지속적인 개발과 연구가 진행 중입니다.

Fan-out

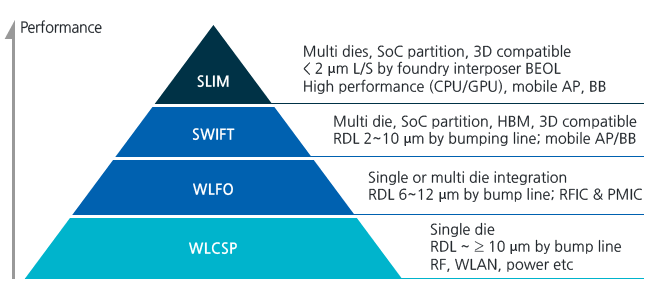

Advanced Wafer Level Fan-out Packages

Amkor에서는 반도체 집적회로의 기능을 극대화하면서도 3차원 집적이 가능한 혁신적인 Fan-out 패키징 기술인 SLIMTM과 SWIFTTM를 개발했습니다. SLIMTM은 Silicon-Less Integrated Module의 약자로, 기존 실리콘 인터포저를 활용해 1㎛ 선폭 수준의 chip 간 연결을 구현하는 패키징 기술입니다. SWIFTTM는 Silicon Wafer Integrated Fan-out Technology의 약자로, 기존 Wafer Level Fan-out(WLFO)나 Wafer Level Package(WLP)의 한계를 뛰어넘어 2㎛ 선폭 수준으로 2개 이상의 반도체 chip을 하나의 패키지에 집적하는 기술입니다.

SLIMTM & SWIFTTM 패키징 기술의 특징

- Polymer-based multi-layer dielectrics

- Multi-die and large die capability

- Large package body capability

- Interconnection density down to 1㎛ (SLIMTM) and 2㎛ (SWIFTTM) line/space

- Cu pillar die interconnect down to 30㎛ pitch

- 3D/PoP capability utilizing Thru Mold Via (TMV®) or tall Cu pillars

Amkor’s Advanced Wafer Product Positioning

LAB

LAB (Laser Assisted Bond) Innovative interconnection solution

1958년 발명된 LASER(Light Amplification by Stimulated Emission of Radiation, 방사의 유도방출에 의한 광의증폭)는 이후 급속한 기술발전과 함께 의료, 군사, 통신, 전기/전자, 자동차, 광학, 엔터테인먼트 등 다양한 산업 분야에서 활용되고 있습니다. 반도체 패키징 분야에도 Laser Marking, Laser Saw, Laser Drilling, Laser Measuring 등에 활용되고 있으며, 나아가 앰코는 Laser Assisted Bond(LAB)를 통한 die to substrate pad interconnection 및 die to die, die to wafer interconnection을 업계 최초로 구현했습니다.

LAB의 기본 원리는 laser oscillator(발진기)를 통해 방출된 laser beam을 광학계를 통과하면서 die 사이즈에 맞는 균일한 laser beam으로 구현하며, 이를 die에 조사해 die와 substrate 간의 접합(Interconnection)을 가능케 합니다. 이러한 LAB의 접합(Interconnection) 방법은 기존 mass reflow(furnish convection을 통한 bonding)의 문제점인 high thermal stress, high warpage를 해결하면서도 생산성을 극대화하는 차세대 접합기술로 떠오르고 있습니다.

Advantage of LAB

최근 반도체 chip의 trend는 thin die, large die, thin substrate, low Si node(28nm, 20nm, 14/16nm, 10nm in 2016)입니다. 이에 따라 packaging process에서의 low thermal stress가 key issue이며, LAB는 최적의 laser energy를 통한 interconnection을 구현함에 따라 thermal stress를 기존 mass reflow 방식보다 70% 이상 줄일 수 있게 됩니다.

활용 분야

Laser Assisted Bond(LAB) 기술의 활용분야는 기존 mass reflow를 적용한 모든 분야를 대체할 수 있으며, 더 나아가 thermal stress에 취약한 low K die, large die, large body, thin die 및 coreless PCB interconnection 등 첨단 packaging 분야에 적용할 수 있는 process입니다.

Application

- Mobile AP

- Server / Network Driver

- MEMS

- Power Management, Baseband

- ASICs and SOCs

- Memory

Strip Grinding

Thin PoP Solution by Strip Grinding

시장의 요구사항에 맞춰 ultra thin PoP package를 제공하기 위해 Amkor는 strip grinding system을 도입했습니다. 즉, strip 상태에서의 PKG를 원하는 두께까지 grinding 하는데, PKG에는 어떤 damage도 입히지 않고 final thickness의 구현이 가능합니다. 또한, 이를 통해서 mold flash로부터 자유로운 exposed die PKG를 제공할 수 있습니다.

Purpose

- To enable ultrathin PoP for exposed PoP structure

- To reduce the total height of a molded strip to achieve target thin thickness without any damage to the PKG

- Narrow mold clearance < 50㎛

- It is feasible to generate mold flash free of exposed die PKG

Status

- Qualification : Completed on Dec. 2014

Strip grinding system

Grinding application

- There was a limitation for ultra thin PoP generation due to severe warpage and process concerns (e.g. thin die handling, narrow mold clearance)

- Strip grinding system enables PKG total height reduction without any damage to PKG

– Thin die < 30㎛

– Narrow mold clearance < V50㎛