Service for Package

Design

Qualified Designers

- 숙련된 수십 명의 designer 구축

- Package별 분업화로 전문인력 강화

- Knowledge와 experience를 바탕으로 한 creativity 창출

- 지속적인 교육훈련 및 designer 인증 프로그램 도입

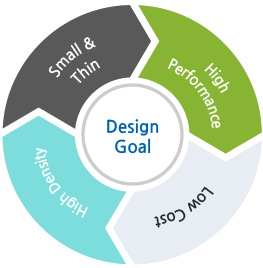

Goal

- 고객과 전략적 협력관계 구축을 통한 business 강화

- High quality, reliable and cost effective design 제공

- 신속한 고객지원 및 고객경쟁력 강화를 위한 서비스 제공

A variety of design experience for advanced Package

- High performance design

- Low cost design

- Optimization form factor design

Design automation tool을 활용한 reliable design service

- Drawing document Automation

- Design utility : Design Rule Checks (DRCs), Design Quick Start (DQS) program, CAM check

- Design tool : Cadence Allegro/APD/SiP, Sigrity UPD, Auto Cad, CAM 350,

L-edit, Creo parameter, Virtual Package

고객 맞춤형 Design Support

- 다양한 Design program tool 확보 및 Export data support

- Smart infra networking 도입 (Auto e-mail service, 화상회의시스템)

- Customer communication channel 운용 (Product Lifecycle Management)

- 초기 Design review report 및 Short cycle time for Quick design support

고객 Requirements support 위한 Design collaboration works

- Co design for Thermal, electrical and mechanical requirement

Layer conversion

- From 2 layer PCB to 1 layer PCB

Electrical matching

- Skew matching

- Differential routing

Process conversion

- From Wire Boning process to Flip chip process

High Quality for design

- Optimization material review

- Perfect design solution for reliability

Characterization

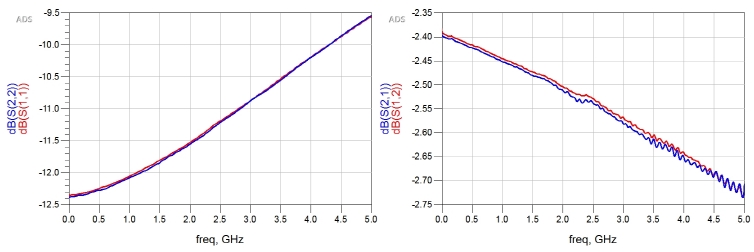

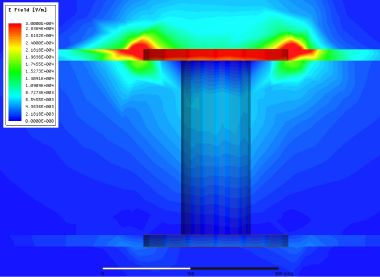

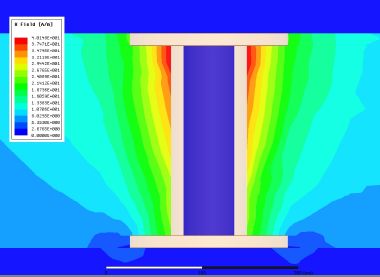

Package는 전기적 측면에서 silicon die와 Motherboard 사이에 interconnection을 위해서 사용되고, 신호를 전달하는 전송선로(transmission line)로 볼 수 있습니다. 최근 전자기기는 고객의 요구를 충족시키기 위해 점차 소형화되고 고속으로 동작합니다. 또한, package 크기와 두께는 감소하고 전송선로배선의 밀도는 증가하고 있습니다. 이 때문에 package level에서 전기적 특성을 분석해 신호전달 손실을 최소화하는 과정은 선택이 아닌 필수가 되고 있습니다.

Amkor는 package에서의 신호전송 손실정도가 고객요구에 만족할 수 있도록 Co-design과 optimization을 지원합니다. 이 과정에서는 주파수영역, 시간영역의 다양한 분석방법이 사용되며, system level 분석에 필요한 결과 파일을 도출할 수 있습니다.

- Lumped RLC and coupling 분석

- S-parameter 분석

- Impedance (Z) and Time Delay 분석

- Touchstone, IBIS and Spice package models 제공

- Power and ground IR drop, current distribution and DC resistance 분석

- Simultaneous switching noise (SSN) 분석

- EYE-Diagram 분석

- EMI / EMC 분석

반도체 패키지는 더욱 작아지고 얇아졌지만 소모 전력은 점점 증가합니다. 그래서 발열 문제는 반도체 패키지의 성능을 좌우하는 중요한 요소가 되었습니다. Amkor는 이러한 패키지 구조에 따른 열 성능을 평가하고 개선하기 위해 많은 노력을 합니다. 패키지의 열 특성 평가는, 고객이 원하는 소모 전력과 발열 성능에 맞는 패키지를 선정하기 위한 것입니다.

패키지 열 성능 분석 (유한 요소 해석 방법)

- QTC : 통계적인 방법을 이용한 패키지 열 저항의 빠른 계산으로 패키지 개발 초기 단계에 적용합니다.

- Web- simulation : 웹 기반에 간편하게 FEA(유한 요소 해석) 할 수 있습니다.

- IcePak : 열 유동해석(CFD) 프로그램을 사용해 패키지 및 시스템 수준의 열 해석을 할 수 있습니다.

패키지 열 성능 분석 (테스트)

- 열 저항 측정 위한 패키지 : 모든 종류의 패키지(wire bond, flip chip)를 제작할 수 있습니다.

- JEDEC 표준 실험 방법 : Theta JA(자연 대류, 강제 대류), Theta JB, Theta JC

- 100Watt 이상 테스트할 수 있습니다.

- MCM, Power map을 적용할 수 있습니다.

Failure Analysis

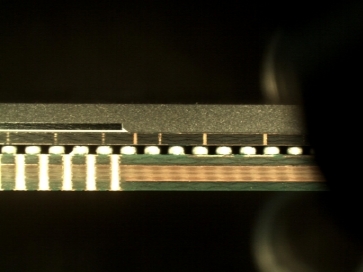

Failure Analysis (FA), 불량 분석

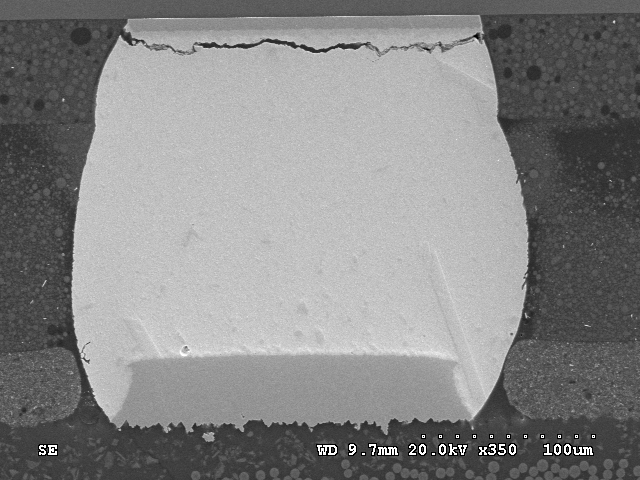

불량 분석(Failure Analysis, FA)은 assembly 도중이나 완료 후, 신뢰성 테스트 후 혹은 board mount 시에 발생하는 불량현상을 다양한 분석방법을 통해 확인하고 원인을 밝혀 해결방안을 제시하는 것을 목적으로 합니다.

샘플처리방법에 따라 비파괴 분석(non-destructive)과 파괴 분석(destructive)으로 나뉘며, 주로 두 방법을 차례로 진행합니다. 비파괴 분석을 통해 일차적인 불량모드와 위치를 확인하고, 파괴 분석을 진행해 불량위치를 드러낸 후, 표면분석장비를 사용해 자세한 불량원인을 조사합니다.

PKG level에서 주요 failure mode로는 open, short, leakage 등이 있습니다.

- 비파괴 분석 방법 : Optical scope, curve trace, SAT, X-ray, 4-probe point, TDR 등

- 파괴 분석 방법 : Polishing, chemical/dry/laser decapsulation, FIB 등

- 표면분석 장비 : FTIR, FESEM, EDX, XPS, AES, SIMS, Interferometer, AFM 등

Material Analysis

Material Analysis (MA), 소재 분석

소재 분석(Material Analysis, MA)은 package에 사용되는 모든 재료의 기본물성을 분석함으로써 package 개발 시 필요한 Material guideline을 제시하고 완성된 package에서 나타날 수 있는 재료측면에서의 문제점들을 사전에 검토하여, 공정 전후 불량률을 줄입니다. 원재료의 QC를 시작으로 공정과정을 거친 재료상태를 가정한 샘플들이 분석되며, assembly 완료 후 package의 특성분석도 진행되고 있습니다.

원재료 QC (Quality control)

- TGA (Thermal Gravimetric Analyzer)

- DSC (Differential Scanning Calorimetry)

- Rheology Analysis : ARES (Advanced Rheometric Expansion System)

공정과정이 고려된 재료물성 분석

- TMA (Thermal Mechanical Analyzer)

- DMA (Dynamic Mechanical Analyzer)

- Rheology Analysis : ARES (Advanced Rheometric Expansion System)

Assembly 완료 후 Package의 특성 분석

- Warpage Analysis : Shadow-moire

- Mechanical Analysis : Instron

BLR test

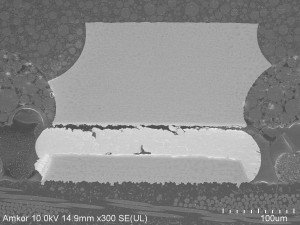

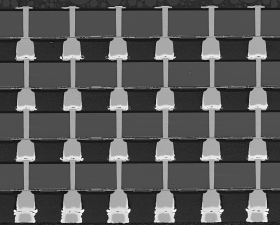

보드레벨 신뢰성은 반도체 패키지에 대한 신뢰성 평가방법 중에 실험용 보드에 패키지를 표면실장한 상태에서 진행하는 것을 말합니다. 전자제품은 최종 사용용도 또는 사용자가 처한 물리적 환경에 따라 다양한 종류의 스트레스가 가해지고, Motherboard(또는 메인보드)에 표면실장한 패키지는 이러한 환경을 모방한 신뢰성 평가결과를 가지고 있어야 고객으로부터 비즈니스를 가져올 수 있습니다. 패키지가 Motherboard에 표면실장하면 반도체 패키지와 Motherboard를 기계적/전기적으로 연결하는 부위가 구조적/기계적으로 가장 취약한 부위로 알려졌고, 이를 ‘Solder Joint’라 부릅니다. 이에 대한 신뢰성 평가를 주로 진행하기에 보드레벨 신뢰성을 ‘Solder Joint 신뢰성 평가’라 부르기도 합니다. 진행 도중 Solder Joint에는 주로 기계적/전기적 파손이 발생합니다.

- 패키지와 실험용 보드가 전기적으로 하나의 회로가 되도록 데이지 체인(Daisy chain) 형태의 디자인을 구성합니다. 가령, 패키지의 1-2번, 3-4번 핀을 연결하고, 반대로 보드는 2-3번, 4-5번 핀을 연결합니다.

- 만들어진 패키지를 실험용 보드에 표면실장합니다.

- 실험용 보드의 전선연결 부위에 전선을 땜납해 보드를 자동저항 측정장비에 연결합니다.

- 자동저항 측정장비를 가동하면서 신뢰성 평가를 시작하면, 전기저항값이 계속 자동측정됩니다. 일정저항 이상의 값이 나오면 이는 패키지와 보드 사이의 Solder Joint가 기계적으로 파손되었음을 의미합니다. 이때의 시간이 해당 패키지의 BLR 수명이 됩니다.

- 온도 사이클 (TC, temperature cycle) : 전자제품의 온도환경 변화를 모사하는 신뢰성 평가

- 낙하 충격 (Drop) : 모바일 제품을 실수로 바닥에 떨어뜨려 회로연결성 고장을 평가하는 방법

- 순환 굽힘 (Cyclic bend) : 모바일 제품을 사용하거나 의복 주머니에 보관해 이동 중 사람의 손가락이나 근육의 주기적인 움직임으로 인한 Motherboard의 스트레스를 모사하는 신뢰성 평가

- 머너터닉 굽힘 (Monotonic bend) : Motherboard 조립 및 검수 과정, 전자제품 포장 및 선적, 설치, 장비이동 등에 의해 발생할 수 있는 한 번의 기계적 충격을 모사하는 신뢰성 평가