안녕하세요, 앰코인스토리 독자 여러분! 완연한 봄이네요. 꽃 피고 따뜻한 날이 많아서, 필자는 겨우내 무거웠던 옷도 정리하고 봄맞이 대청소도 하면서 조금씩 봄을 즐기고 있습니다. 지난달에 언급했던, 원가절감에의 노력에 대한 이야기를 이어가겠습니다. 지난 호에는 재료에 대해 살펴봤다면, 이번에는 제조공정과 패키지 구조에 대해서 알아보도록 하겠습니다.

대면적화

반도체 장비들은 대부분 1년 365일 멈추지 않고 가동됩니다. 간혹 뉴스에서 반도체 공장에 정전이 발생해 큰 손해를 봤다는 소식을 접할 수 있는데요, 그만큼 세밀하고 민감한 공정이라 장비 역시 일정한 상태를 유지해야 합니다. 그래서 꺼지지 않고 항상 유지가 되어 있어야 하지요. 장비가 쉬지 않고 가동되고 있다면, 같은 시간 내 더 많은 제품을 생산해야 원가절감을 할 수 있습니다. 어떻게 하면 더 많은 제품을 생산할 수 있을까요?

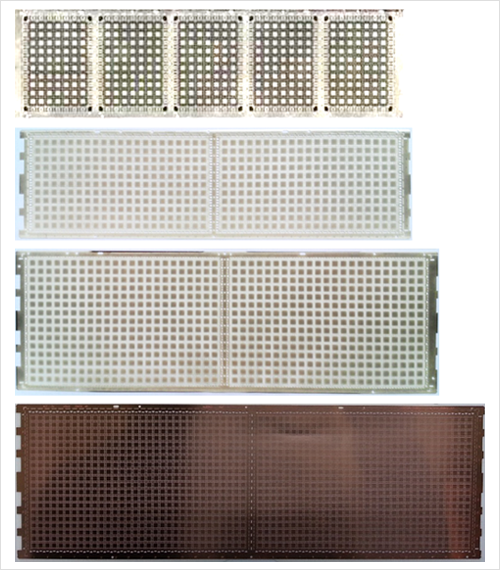

첫 번째는 기판의 대면적화입니다. 말이 좀 생소하게 들릴 수 있지만 쉽게 말해 한 번에 많이 만들 수 있도록 넓은 면적의 기판을 사용하는 것입니다. 최종 제품의 크기는 작게는 수 mm에서, 크게는 수십 mm에 이릅니다. 그런 제품을 낱개로 작업하지 않고 여러 개가 배치된 스트립으로 만들어서 작업합니다. 일반적으로 패키징의 모든 공정은 스트립 단위로 이루어집니다. 와이어 본딩이나 플립칩 본딩을 시작해서 모든 공정이 마치기까지 스트립 단위로 공정이 진행되는데요, 앞서 설명한 대로 스트립 크기가 넓어져서 더 많은 패키징 개수를 한 번에 처리할 수 있다면, 공정 비용을 낮출 수 있습니다. 아래 그림은 <리드프레임 패키지의 스트립>입니다. 크기가 점점 더 커지면서 배치된 패키징 개수도 더 많아졌음을 알 수 있습니다. 그렇다면 여기서 질문이, 스트립 크기가 클수록 좋다면 지금보다 두 배 세 배 더 크게 만들면 되지 않을까요?

▲ QFN strip size

딱 잘라 말해, 그렇게 되면 패키징 공정이 어려워집니다. 몰딩 공정을 생각해 볼까요? 그림을 보면, EMC가 녹아서 금형 한쪽 끝에서 흘러들어 가서 빈 곳 없이 구석구석을 채우는데, 경화도 같이 진행됩니다. 요즘은 패키징 두께도 점점 얇아져서 EMC가 흘러가는 공간도 좁아지는데 전보다 더 먼 거리를 흐르면서 모든 공간을 채우는 것도 더 어려워지겠지요. 그래서 새로운 EMC를 개발하고 몰딩을 하는 장비도 그에 걸맞게 개선되어야 합니다.

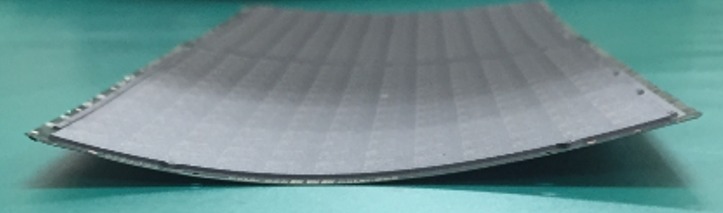

몰딩을 해결했다고 해서 끝이 아닙니다. 스트립 크기가 커진 만큼 변형, Warpage도 같이 커질 수 있습니다. Warpage가 커지면 솔더볼을 붙일 때도 각각의 패키지로 자를 때에도 공정에 어려움이 따릅니다. 하지만 이 모든 수고를 통해 가격 경쟁력을 가질 수 있기에 계속 연구를 이어가고 있는 것이지요.

▲ Mold flow behavior in strip

▲ 몰딩 공정 후의 스트립 Warpage

패키징 구조

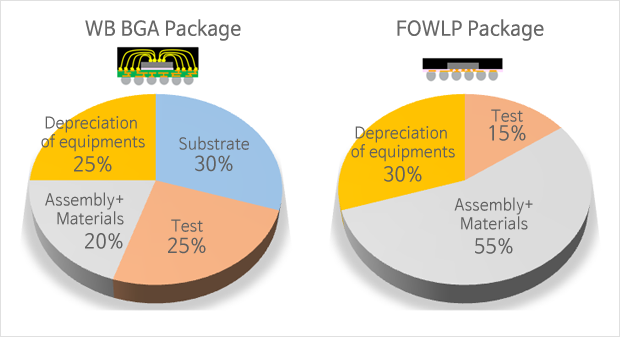

패키징 가격의 상당 부분은 기판(Substrate)이 차지합니다. 원가절감의 또 다른 시도는 기판의 가격을 낮추기는 데에 멈추지 않고 기판 자체를 생략하는데 이르렀습니다.

▲ 패키징 원가 구조 비교

사진출처 : https://goo.gl/yoYL4F

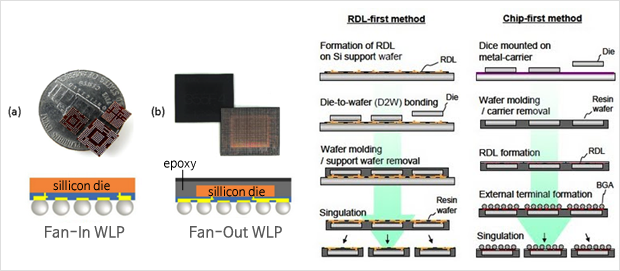

국내 외의 기판 제작 업체에서 만든 기판을 사용하지 않고, RDL (Redistribution Layer) 공정을 통해 패키징 업체에서 직접 기판을 제작하는 방식입니다. 이런 종류의 패키지를 WLP (Wafer Level Package)라고 부릅니다. Pre-preg와 Core 대신에 수 um 두께의 RDL, Passivation 등으로 기존의 Laminate 기판을 대체할 수 있습니다. 아울러 I/O 개수가 증가하는 추세를 따라잡기 위해 칩 크기보다 큰 FOWLP (Fan-out WL)에 대한 관심이 더 증가하고 있습니다.

▲ (좌)Fan-in vs Fan-out WLP 비교/(우)FOWLP 제조과정

사진출처 : (좌)https://goo.gl/xgJy1b/(우)https://goo.gl/RmNUcn

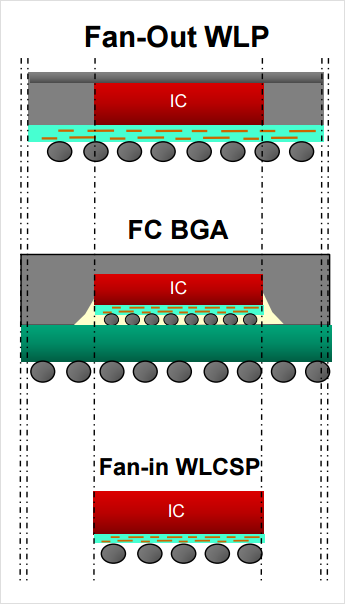

FOWLP의 장점은 기판 비용이 없어서 원가절감을 기대할 수 있습니다. FCCSP에 비해 Cu pillar 혹은 솔더범프와 같은 chip과 기판 사이의 Interconnection도 생략할 수 있습니다. 기판이 없기에 더 얇은 두께도 구현할 수 있습니다. 기판을 구성하는 두꺼운 절연체(pre-preg, Core)가 없기에 방열 효과 개선도 기대할 수 있습니다.

▲ FOWLP와 경쟁 패키지 사이즈 비교

사진출처 : https://goo.gl/yoYL4F

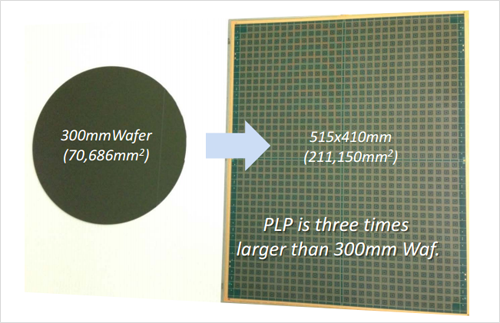

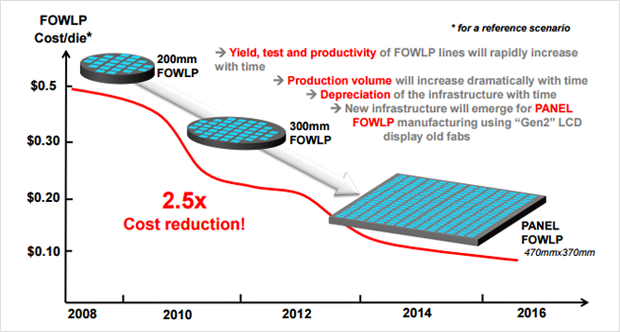

이렇게 기판을 생략하면, 당연히 기판을 생산하는 업체 입장에서는 고민을 넘어서 생존을 걱정해야 할 처지입니다. 국내외 기판 제조 업체에서 FOWLP에 대항할 수 있는 Panel FOWLP 개발하는 중인데요, FOWLP는 공정의 기본 단위인 Wafer 크기가 제한되어 있습니다. 현재 12인치 크기인데, 이보다 더 큰 Wafer 적용은 현실적으로 많은 어려움이 있습니다. Wafer 크기에 제한된 WLP 대신에 Panel FOWLP는 PCB기판을 사용하므로 Wafer보다 더 큰 면적을 사용할 수 있습니다. 아래 그림에서는 12인치 웨이퍼에 3배에 해당하는 면적으로 패키징할 수 있습니다. 원형의 Wafer에 비해 사각형의 Panel이 면적 활용율에 훨씬 좋습니다. 공정상에 발생할 수 있는 문제만 잘 해결된다면 WLP에 비해 분명 가격 경쟁력이 있는 것으로 평가되겠지요.

▲ Wafer와 Panel 면적 비교

사진출처 : https://goo.gl/mkKmmZ

▲ Wafer 및 Panel면적에 따른 원가 비교

사진출처 : https://goo.gl/yoYL4F

마무리하며

두 번에 걸쳐서 패키징에서 원가절감을 위해 어떤 노력과 연구를 하는지 살펴보았습니다. 아무래도 사람 마음은 조금이라도 더 싼 가격을 찾기 마련입니다. 어제보다 오늘에는 더 나은 기능과 더 낮은 가격을 기대하며 전자제품이 전시된 곳을 사람들은 유심히 쳐다보고 있습니다. 한 번에 끝나지 않고 패키징 업체의 숙명과도 같다고 생각합니다. 원가절감의 관점에서 패키징을 이해하는데 도움이 되었기를 바랍니다.

다음 호에는 또 어떤 이야기를 이어 나갈지 또 고민 속으로 빠져들 것 같군요! 부족함에도 제 이야기에 관심 가져 주시는 분들이 많으시더라고요. 좀 더 재미있고 유익한 내용으로 다시 찾아뵙겠습니다. (응원댓글은 언제나 환영입니다)

WRITTEN BY 정규익

청운의 푸른 꿈을 안고 앰코에 입사한 지 어느덧 만 10년이 되었군요. 10년이면 강산도 변한다는데 마음만은 늘 신입사원처럼 모든 일이 신기하고 궁금해서 즐겁게 일했으면 하는 바람입니다.