지난 호에서는 ‘반도체의 역사’라는 주제로 반도체의 기술적 정의와 발전 과정을 살펴보았다. 이번에는 ‘반도체의 현재’라는 주제로 시작해 보려고 한다. 그래서, 지금 반도체 제조회사들이 반도체의 집적도를 더욱 높이고 한계를 극복하기 위해 사용하거나 연구하는 그 기술들에 대해 살펴보고자 한다.

우리가 살 수 있는 면적은 제한적이다. 처음에는 전원주택과 같은 여유로운 주거 환경에서 점점 인구가 증가함에 따라 주택가 같은 밀집 지역이 생겨나고, 이어 5층 안팎의 연립주택으로, 또다시 10여 층 이상의 아파트단지로, 이제는 그 아파트들이 20층을 넘어 50층 이상의 초고층 아파트로 등장하기에 이르렀다. 하지만 기술의 한계로 무한정 높게 쌓을 수는 없고, 언젠가는 그 높이도 한계에 다다르게 될 것이다. 아마도 그때는 바다나 우주와 같은 또 다른 공간을 찾는 시도를 할지도 모르겠다.

반도체도 이와 비슷하다. 제한된 면적에 트랜지스터의 크기를 작게 만들어 집적도를 높이는 방법은 그동안 매우 효과적인 방법이었다. 하지만 현재에 이르러서는 그 한계를 맞고 있는 듯하다.

무어의 법칙과 황의 법칙

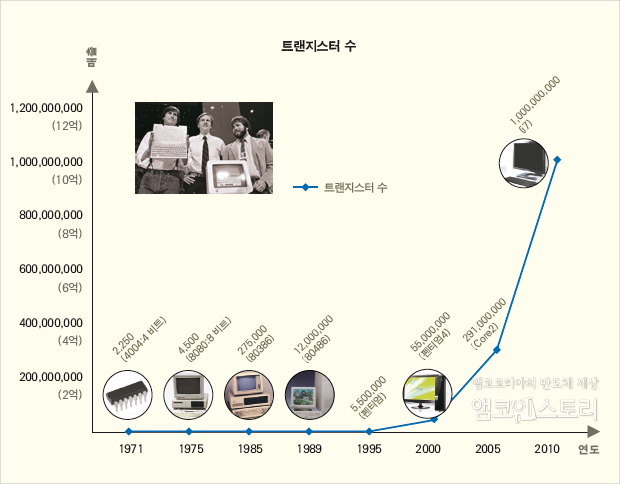

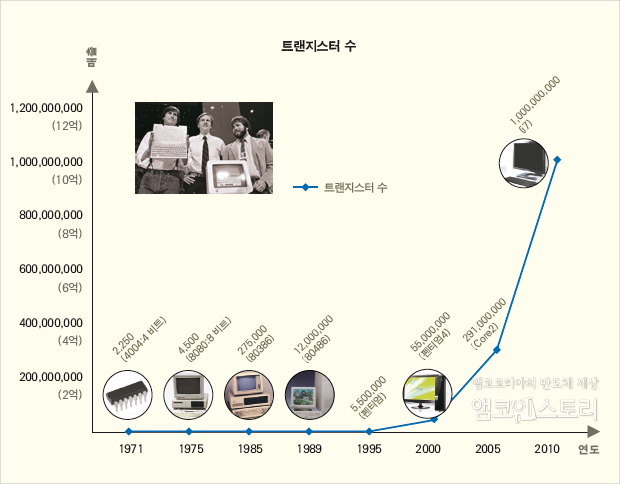

1940년대에 반도체가 처음 발명되고, 1960년대에 집적 반도체가 처음으로 상용화된 이후, 반도체는 실로 눈부시고 숨가쁘게 발전되어 왔다. 인텔사의 공동 설립자이자 반도체 과학자였던 고든 무어(Gordon E. Moore)는 1년 6개월마다 반도체의 성능이 두 배로 개선이 된다는 ‘무어의 법칙(Moore’s Law)’을 발표했고, 정말 30년 동안은 법칙으로 지켜지는 듯했다.

하지만 2000년대에 들어서자 삼성은 무어의 법칙을 깨고 자신들은 1년마다 두 배로 개선하겠다는 이론을 펼쳤고, 삼성전자 황창규 사장의 성을 따 ‘황의 법칙’이라고 이름 지었다.그리고 이것을 실제로 실현함으로써 결국 삼성은 세계 반도체 시장 메모리 분야에서 세계 1위의 독보적 위치를 차지하게 된다.

어쩌면 1년 6개월 혹은 1년이라는 이런 법칙 때문에 반도체가 필연적으로 스스로 발전했다기보다는 목표를 세우고 이를 위해 부단하게 노력해온 우리 반도체업계 종사자들이 흘린 땀 때문에 발전할 수 있었다고 보는 것이 옳을 것이다.

여하튼 오늘날까지 반도체의 발전은 트랜지스터 크기를 줄여 제한된 면적에 더욱 많은 트랜지스터를 집어넣어 집적도를 높이는 방법으로 발전되어 왔다. 이와 같은 개발 방법은 지금까지 매우 효과적이었고, 그래서 무어의 법칙이든 황의 법칙이든 가능했었다. 1960년대 여유로운 시골 마을에서, 1970년대 밀집한 주택가, 1980년대 5층짜리 연립주택들, 그리고 2000년대 엘리베이터가 설치된 아파트 단지들까지, 이들 건물은 무어의 법칙처럼 1년 6개월만에 전국에 수백 수천 개씩 대량으로 빠르게 지어졌다. 지금은 40층 이상의 초고층 아파트들이 지어지고, 심지어는 100층이 넘는 건물도 지어지는 중이다.

문제는 이와 같은 초고층 아파트는 20층 남짓한 아파트를 지을 때 사용하던 시멘트와 같은 재료와 기존 건설 공법으로는 만들 수 없다는 점이다. 그래서 새로운 건축 재료와 공법이 필요하게 되었다. 이처럼 반도체 개발에서도 지금까지 해온 것처럼 단순하게 크기만을 줄여 집적도를 높이는 고전적인 방법으로는 한계에 봉착한다. 그래서 한계에 다다른 무어와 황의 법칙을 이어가기 위해서는 새로운 재료와 기술이 필요하게 된 것이다.

유전율과 FIN-FET

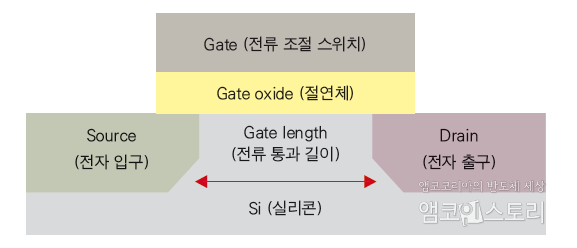

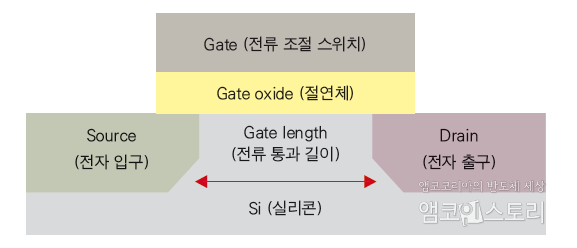

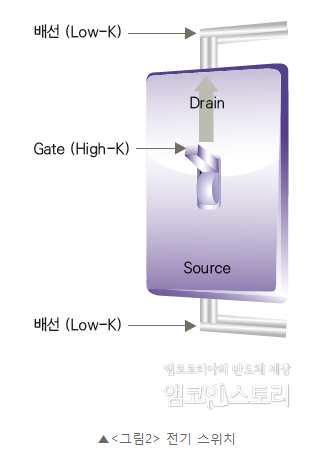

다소 어려울 수도 있겠지만, 반도체의 집적도를 이해하기 위해서는 트랜지스터 구조를 이해해야 한다. 반도체, 즉 트랜지스터에는 아래와 같이 회색으로 칠해진 실리콘에 전자 흐름의 입구라 할 수 있는 ‘소스(Source)’와 전자 흐름의 출구라 할 수 있는 ‘드레인(Drain)’이 있다. 습기가 있는 곳에 철을 두면 그 표면에 녹슬어 산화철이 만들어지는 것처럼, 실리콘을 고온으로 가열하면 표면에 녹슬어 산화실리콘이라는 물질로 바뀐다. 이 산화실리콘은 반도체의 특성을 잃어버리고, 전혀 전기가 흐르지 못하는 절연체가 된다.

▲<그림1> 반도체 실리콘 구조

지난 호에서 반도체에 자극을 주어 도체 혹은 부도체가 되도록 조절할 수 있다고 설명한 바와 같이, 이 산화실리콘 위에 자극을 주기 위한 스위치 역할을 해주는 게이트(Gate)를 연결하게 된다.

앞서 설명한 반도체의 집적도를 높이는 방법으로 트랜지스터를 작게 만든다고 했는데, 그것이 바로 위의 그림에서 빨간색 화살표로 표시된 ‘전류 통과 길이’인 ‘게이트렝스(Gate length)’를 작게 하는 것이다. 그래서 이 거리를 숫자로 표시한 것이 32나노 혹은 20나노 반도체 디바이스라고 한다. 1나노(nm, Nano meter)는 1mm의 백만분의 1이다. 1mm도 작은데 그것의 백만분의 1이라니. 언뜻 느낌이 오지 않는다. 예를 들어 보자. 우리 키가 1m라고 해보자. 만약 이 키를 백만배 키우면 얼마나 될까? 1,000km가 될 것이다. 키가 1,000km면 우리나라 해남 땅끝마을에서 시작해 북한 백두산을 지나 한반도 북쪽 끝 두만강에 이르는 거리다.

자, 다시 반도체로 돌아오자. 반도체의 가장 중요한 기능 중의 하나가 스위치 기능이다. 그럼 어떤 스위치가 좋은 스위치일까? 첫 번째, 스위치를 켜고 끌 때 그 전류의 흐름을 빠르게 연결하고 빠르게 끊어야 할 것이다. 두 번째, 스위치를 켰을 때 전류가 끊김없이 잘 흘러야 하며, 껐을 때는 전류가 전혀 흐르지 않아야 한다. 세 번째, 그 스위치를 켜고 끌 때 적은 힘으로도 부드럽게 켜고 끌 수 있다면 더욱 좋을 것이다.

그럼 반도체 트랜지스터 스위치에 있어서 위와 같은 성능을 높이는 방법에는 무엇이 있을까? 트랜지스터의 성능을 높이는 가장 일반적인 방법은 두 가지가 있다. 첫 번째는 전자입구인 소스에서 전자출구인 드레인까지, 전류통과 길이인 게이트렝스를 줄이는 방법이다. 두 번째는 위의 그림에서 검은색으로 칠해진 절연체(gate oxide)의 두께를 줄이는 것이다.

이 두 가지 방법을 통해 트랜지스터 스위치를 조절하면서 게이트에 아주 작은 전류 자극을 걸어도 소스와 드레인 간의 적은 전류 흐름까지도 매우 빠르게 조절할 수 있게 된다. 만약에 이 반도체가 휴대전화에 사용된다면, 적은 전류로 트랜지스터들이 작동하기 때문에 결과적으로 배터리 소모를 줄여 한번의 충전으로 더욱 오랫동안 사용할 수 있게 한다. 그리고 게이트 렝스를 줄이면 트랜지스터 스위치의 성능을 높이는 것은 물론, 앞서 말한 반도체의 집적도를 높이는 방법이기도 해서 일거양득이 된다. 그래서 반도체 업계들이 끊임없이 게이트 렝스를 줄이고자 노력해 왔다.

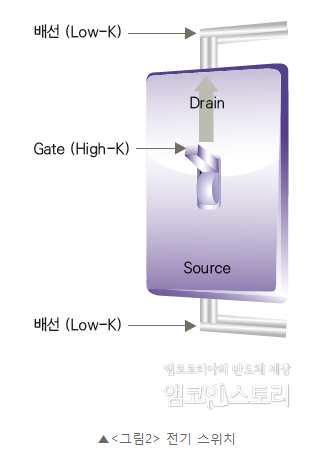

그런데 이렇게 1960년대 반도체가 상용화한 후 40년이 지난 현재까지도 끊임없이 줄이다 보니 이젠 너무 작아진 게이트렝스가 다른 문제점을 유발하는 부작용이 나타나기 시작했다. 즉, 소스와 드레인 간의 서로 거리가 너무 가까워지다 보니,게이트에 전류 자극을 주지도 않았는데도 이들 사이에 조금씩 전류가 흐르는 ‘누설전류’가 나타나기 시작한 것이다. 게다가 그 반도체에는 수억 개의 트랜지스터가 집적되다 보니, 그 누설전류들 역시 무시할 수 없는 수준이 되었다. 마치 우리가 휴대전화를 사용하지 않는 대기 상태에서도 누설전류에 의해 계속 배터리를 소모하게 되는 원인이 되는 것처럼 말이다.

그래서 반도체 제조업체들은 게이트 렝스를 줄이고 게이트 절연체 두께를 얇게 만들어도 누설전류가 최소화되는 방법을 연구하기 시작했다. 이들 문제에 대항하고자 근래에 들어 등장한 대표적 기술들이 ‘High-K’와 ‘Fin-FET’다.

글쓴이 / 기술연구소 개발2팀 김윤주 부장