지난 열 달 동안 반도체의 물리적 이론과 소자의 이해 및 최종 제품에 대해서 살펴보았는데요, 이제 이 제품들이 제조라인에서 어떻게 만들어지는지에 대해 살펴보도록 하겠습니다.

하나의 반도체 제품이 탄생하기까지는 수많은 과정을 거쳐야 합니다. 여기에서는 설계 등은 고려하지 않고 공정에 대해서만 살펴보고자 합니다. 공정은 크게, 웨이퍼 제조 공정, 소자(디바이스) 제조 공정, 그리고 마지막으로 우리 회사가 가장 잘하는 패키징 및 테스트 공정으로 나눌 수 있습니다. 이 중에 웨이퍼 제조 공정은 이전 호에서 다루었으므로 소자 제조 공정과 패키징 및 테스트 공정에 대해서 다루겠습니다. 반도체 소자도 여러 가지가 있지만, 가장 많이 생산되고 있는 MOSFET 소자의 공정에 대해 살펴보겠습니다.

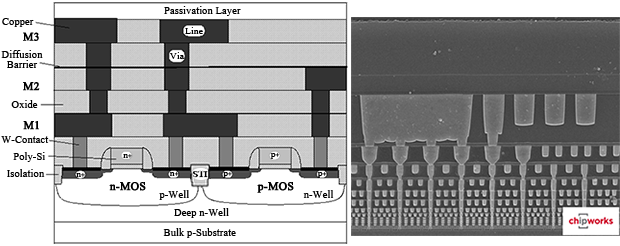

소자 제조 공정은 다시 FEOL(front end of line) 공정과 BEOL(back end of line) 공정으로 나뉩니다. FEOL 공정은 실리콘 에피택시(박막 제조에서 기판 재료 표면의 원자 배열에 의존한 결정 구조의 박막이 성장하는 과정을 말합니다) 층 위에 MOSFET 트랜지스터를 형성하는 단계이고, BEOL 공정은 MOSFET 트랜지스터 위에 인터커넥션을 위한 금속배선 및 입출력 단자를 형성하는 단계를 말합니다.

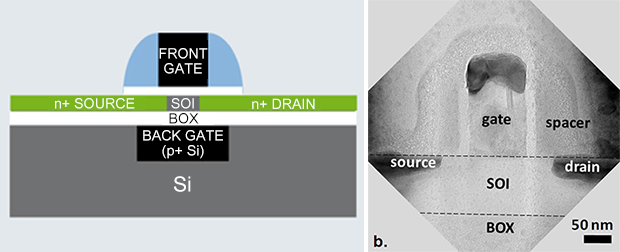

먼저, MOSFET 트랜지스터를 어떻게 구성하는지 살펴봅시다. P 채널 MOSFET 트랜지스터를 가정하면, p형으로 도핑된 기판 위에 게이트 유전층(이산화규소가 일반적으로 사용됩니다)을 형성하고 게이트 영역과 소스 및 드레인 영역을 패터닝(포토마스크 공정으로 각 영역을 정의해 줍니다)한 후 소스와 드레인 영역에 n형 도펀트(5가의 원자가를 갖는 불순물)를 도핑(임플란테이션이나 확산 공정을 통해 도핑합니다)함으로써 형성됩니다.

▲ (좌)MOSFET모식도 (우)투과전자현미경사진

이미지출처 : (좌)http://goo.gl/1HRNcg (우)http://goo.gl/tvvuAu

MOSFET 트랜지스터가 형성되었으면, 이들의 인터커넥션을 통해 원하는 회로를 형성해야 합니다. 인터커넥션은 일련의 BEOL 공정 단계(금속배선과 유전층에 의한 절연 공정을 반복해서 진행합니다)를 통해 몇 층의 금속배선을 형성합니다. 초기의 배선은 주로 알루미늄을 통해 이루어졌습니다. 시간이 흐르면서 같은 칩 면적 안에 더 많은 트랜지스터를 집적시키기 위해 트랜지스터 크기가 줄어들고 트랜지스터 간의 간격도 줄어들게 되었지요. 공정이 미세화됨에 따라 더 많은 트랜지스터가 동일 크기의 웨이퍼 내에서 형성되므로 공정 가격이 내려가고(웨이퍼당 가격은 올라가더라도 트랜지스터 하나당 가격이 내려간다는 의미이니 혼동하지 마세요) 소자의 성능은 향상되었습니다(소스와 드레인 사이의 간격이 줄어들면서 캐리어가 채널을 통과하는 데 걸리는 시간이 짧아지므로 신호는 더 빨라지는 셈입니다. 더구나 트랜지스터 간의 간격도 줄어들었으므로 트랜지스터 간의 신호전달도 더 빨라졌지요).

하지만 늘 좋은 일만 있는 것은 아니지요. 역기능도 나타나기 시작했답니다. 트랜지스터 크기와 간격만 줄어드는 것이 아니라 인터커넥션의 금속배선 크기와 배선 간의 간격도 줄어들어야 합니다(축소복사를 생각하면 됩니다). 전류가 흐르는 금속배선의 유효단면적(전문 용어가 나왔다고 당황하지 마세요, 차가 달릴 수 있는 도로의 폭이라고 생각하면 됩니다)이 줄어들면서 저항이 증가합니다. 소자의 성능은 향상되었지만 인터커넥션에서는 오히려 신호전달에 지연이 초래되었지요.

그뿐만 아니라 저항이 증가하면 열이 발생한다고 했지요(10월호(바로 가기)에 MP3 볼륨을 낮추는 것은 저항을 늘려서 신호 크기를 줄이는 것이고 줄어든 신호는 열의 형태로 전환된다고 설명했습니다), 이 열은 electromigration(전도전자와 금속 속에 흩어져 있는 원자핵들 사이의 운동량 변화로 인해 발생하는 도체 내의 지속적인 이온의 움직임에 의한 물질의 이동을 지칭하는 용어입니다.

역시 어렵지요? 그냥 좁은 금속배선에 높은 전류가 흐를 때 금속 원자가 한 방향으로 이동해서 결국 금속배선을 끊어버리는 현상이라고 이해하면 됩니다. 그런데 이 현상은 온도가 높으면 더 심해집니다)이라는 불량을 더 촉진하였습니다. 문제가 있다고 좌절할 수는 없지요. 금속배선이 알루미늄으로부터 구리로 진화가 이루어졌습니다. 구리는 알루미늄보다 전기전도도가 높고 더 높은 온도에서 녹습니다. 따라서 금속배선 크기가 줄어들면서 발생한 저항의 증가를 늦출 수 있게 되었고 electromigration 문제도 해결했습니다. 모든 문제가 다 해결된 것은 아닙니다.

이번에는 배선 간의 줄어든 간격이 문제가 되었습니다. 도선에 흐르는 전류는 주변에 자기장을 형성한다는 것은 중학교 때 배운 물리 상식이지요. 자기장 속에 있는 도선은 자기장의 변화로 전류가 생성됩니다. 즉, 자기장의 변화로 원치 않는 전류가 생길 수 있다는 말이지요. 도선과 도선이 멀리 떨어져 있으면 서로의 존재를 크게 느끼지 못할 텐데, 가깝게 접근하게 되면 사정이 달라집니다. 서로의 존재를 강하게 느끼게 되겠지요.

그게 무슨 문제냐 고요? 요즘 아파트에서는 층간 소음 문제가 심각한 것 같습니다. 우리 가족만의 독립된 공간을 보장받고 싶은데, 이웃사촌의 발걸음 소리, 노랫소리, 문 여닫는 소리, 심지어는 싸우는 소리도 들리네요. 어떻게 하면 좋을까요? 예, 좋은 흡음 재료를 사용하면 됩니다. 인터커넥션 사이의 간격을 유전상수가 낮은 유전체 재료로 절연을 해주면 간격이 좁더라도 서로의 존재를 크게 느끼지 않는답니다. 이렇게 low-k dielectric 층(low-k dielectric 층은 일반적으로 기계적인 특성이 약해서 잘 깨진답니다. 이 때문에 소자의 신뢰성 문제가 야기되기는 하지만 여기서 깊이 다루지는 않겠습니다)이 소개되었답니다.

물론 low-k dielectric 층을 모든 배선 층에 적용하는 것은 아니랍니다. 배선 간의 거리가 미세한 트랜지스터 인근의 층들에만 low-k dielectric 재료로 절연하고 배선 간의 거리가 충분한 층들에는 일반적인 dielectric 재료로 절연해준답니다. 인터커넥션이 완료된 후에 외부 세계와의 연결을 위해 입출력 단자를 형성해 줌으로써 BEOL 공정이 마무리됩니다.

▲ (좌)MOSFET 모식도 (우)주사전자현미경사진

이미지출처 : (좌)http://goo.gl/GdeUSK (우)http://goo.gl/xCLzgA

간단하지요? 디바이스 제조는 몇 개의 주요 공정의 반복으로 이루어집니다. 주요 공정 사이에 진행하는 세정(cleaning)이나 플라즈마 애슁(ashing) 등의 공정들도 매우 중요한 공정이지만, 전체적인 공정 이해를 위해서 꼭 필요한 공정들만 소개하도록 하겠습니다.

먼저, 패터닝을 위한 포토리소그래피와 식각(蝕刻, etching)을 생각해볼 수 있고, 도핑을 위한 이온 임플란테이션, 박막 형성을 위한 성막(成幕, deposition), 기타 열공정(熱工程)과 평탄화(平坦化, CMP) 공정을 생각해 볼 수 있습니다.

“여기를 보세요, 김치~! 하나둘셋, 찰칵!” 순간을 영원으로 바꾸거나 시간을 멈추게 하는 방법은 바로 ‘사진’입니다. 우리는 기억하고 싶은 순간을 사진을 찍어 보관하지요. 처음 필자의 집에 이사 온 토리의 기념사진입니다. 귀엽지요? 그래도 한 성질 한답니다. (다음 호에 계속)