[건강한 반도체 이야기] 미모와 체중에 신경 쓰는 패키지

안녕하세요? 독자 여러분! 올해 앰코인스토리 [반도체 이야기]의 주제는 ‘건강하고 다재다능한 반도체 이야기’였습니다. 기억하시나요? 지금까지 다섯 차례에 걸쳐 반도체의 건강에 관해 이야기를 했습니다. 자, 이번 호부터는 건강은 기본으로 하고 다재다능한 반도체 이야기를 해볼까 합니다. 갑자기 이런 말이 생각나네요. 아빠가 딸 아이에게 “못생겨도 좋다. 공부 못 해도 좋다. 건강하게만 자라다오!” 과연 진심일까요?

저도 엄마지만 앞의 아빠처럼 훌륭한 부모는 아닌가 봅니다. 저는 솔직히 제 아이들이 건강은 당연하고 부모 유전자의 한계가 있음에도, 이왕이면 키도 크고 예쁘고 날씬하고 공부도 잘했으면 좋겠거든요. 당연히 부모의 욕심이지요. (^^) 반도체 패키지의 성능에 대한 소비자와 고객들의 욕심도 이와 같다고 생각합니다. 건강하기만 하면 안 됩니다. 작아져야 하고, 가벼워야 하고, 얇아져야 하고…. 반도체의 외모가 아주 중요해졌습니다.

스마트폰을 예로 들어 볼까요? 스마트폰 전체 두께는 얼마나 될까요? 지금 여러분 손에 들려있는 폰을 한 번 보세요. 대략 7~8mm 됩니다. 무게는 얼마나 될까요? 기기나 크기에 따라 다르겠지만 대략 150~250g 정도입니다. 이 정도 두께와 무게라면 그 안에 들어가는 반도체 패키지의 두께나 무게는 얼마나 될까요? 제가 지금 지면이 아닌 강의를 한다면 돌발 퀴즈를 내어 가장 근접하게 맞추시는 분께 시원한 아이스크림을 드리고 싶습니다만, 아쉽네요. 아! 댓글을 달아보시겠어요? 하하! 답을 말씀드릴게요.

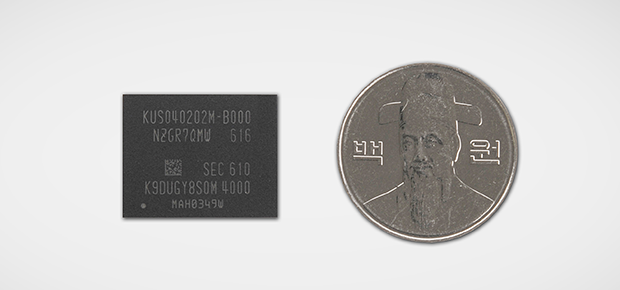

두께는 1mm가 넘지 않습니다. Substrate 기판을 사용하는 Laminated 패키지 타입은 대략 0.5~0.7mm 정도이고 기판을 사용하지 않는 Wafer level CSP 패키지는 보통 0.3~0.4mm 정도 됩니다. (제가 여기서 말씀드리는 수치는 어디까지나 대략적인 수치입니다. 이보다 더 얇거나 두꺼울 수 있으니 참고하시기 바랍니다.) 무게는 얼마나 될까요? 15mm 정도 크기의 패키지는 2g 내외입니다. 이보다 작은 패키지는 물론 그 이하일 것입니다. 최근 삼성전자에서 20mm 512GB 메모리를 1g으로 만들었다고 하네요. 아래 그림에서 보듯, A4용지 1장이 5g 정도 하니 얼마나 가벼운지 감이 오겠지요.

▲ 삼성전자, 무게 1g 크기 2cm ‘512GB BGA NVM2SSD’

사진출처 : 삼성전자

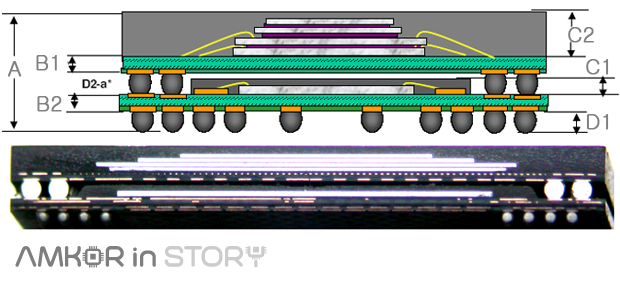

이번에는 그럼 패키지 속으로 들어가 보겠습니다. Mobile Application Laminated 타입 패키지 안에 있는 Si chip 의 두께는 얼마나 될까요? 대략 50~100㎛ 이내입니다. 여러분! 100㎛ 정도면 어느 정도인지 혹시 감이 오시나요? A4 종이 1장의 두께가 80~100㎛ 정도라고 하니, 50㎛ 정도의 Chip 두께라면 A4 종이보다 더 얇은 거겠지요. 아래 그림에서처럼 스마트폰에 들어가는 AP (Application Processor) device이고 패키지 형태는 POP (Package On Package) 입니다. 아래 패키지가 Logic device, 위 패키지가 memory device입니다. 두 개의 패키지가 stack 되었어도 전체 두께가 1mm가 채 안 되지요. 단면을 보시면 Si chip 두께를 대략 가늠해 볼 수 있을 겁니다.

▲ 1mm 이하 두께의 POP (Package On Package) 패키지 단면 사진

패키지 만병의 근원

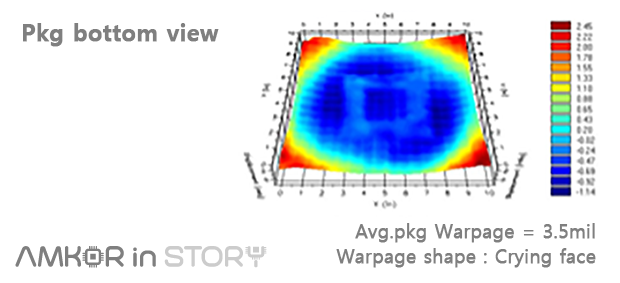

사실 여기까지는 반도체 패키지에 관해 관심이 있으시다면 이미 이 정도는 알고 계신 분들이 많을 겁니다. 멀리 돌아왔는데요, 사실 반도체 외모에 대해 제가 말하고 싶었던 것은 두께나 무게나 크기가 아닙니다. 스마트폰에 들어가는 AP (Application Processor) 패키지는 크기가 대략 14mm 내외입니다. 헌데 chip 성능상 크기를 줄이는 데 한계가 있습니다. 그런데 1mm 이하로 얇아지면서 생기는 문제가 아래 그림들과 같은 패키지 변형입니다. 이것은 Warpage 라고도 하는데요, 이 변형 정도, 즉 warpage 정도가 크면 클수록 문제를 일으킵니다. 어찌 보면 패키지 만병의 근원이라고도 볼 수 있습니다. 그래서 신규 패키지 개발이나 생산 때면 이 Warpage 최소화를 위해 최적화된 구조 설계, 최적화된 재료 선정, 적절한 공정 선택과 조건 설정이 주요 과제가 됩니다.

▲ 패키지 Warpage 측정 결과

패키지 Warpage가 크면 발생하는 문제

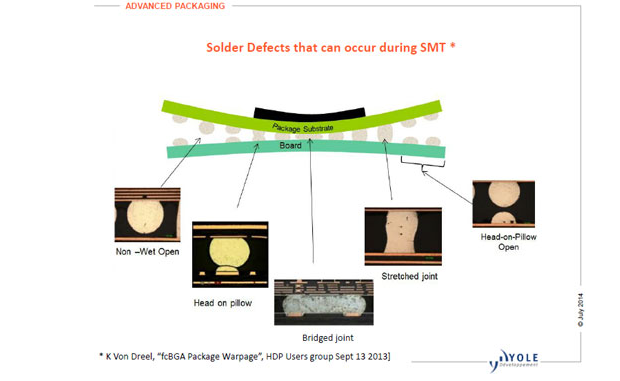

패키지 변형인 Warpage가 크면 무슨 문제가 일어날까요? 일차적으로 패키지를 Board에 실장할 때 Warpage가 과도하면 아래 두 그림에서 보여주는 것처럼 Solder 접합부가 보드에 안 붙는 non-wetting 현상으로 open 불량을 가져오기도 하고 인접한 Solder Ball끼리 녹아 붙으면서 연결되지 말아야 할 회로가 연결되어 short 불량을 일으키기도 합니다.

이차적으로는 패키지가 보드에 실장되고 사용 환경에서 고온, 저온을 겪게 되면 이러한 Warpage 변형 모양이 아래로 불룩(Smile face)하거나 위로 불룩(Cry face)한 모양으로 반복적으로 바뀌고, 이러한 반복적인 변형이 패키지 내부 접착 계면에 박리를 유발하기도 하고 패키지 내부 crack이나 보드와의 전기적인 Solder 접합부 파손으로 Device 본래의 기능을 갖지 못하게 될 수도 있습니다.

▲ 과도한 Smile face Warpage로 인한 SMT공정 중 발생할 수 있는 open / short 불량

사진출처 : Chip Scale Review Magazine (http://goo.gl/UjYbty)

▲ 과도한 Cry face Warpage로 인한 SMT 불량

사진출처 : 특허청 (http://goo.gl/KzHGfC)

패키지 warpage 레벨 요구 조건

과연 실장 때 불량을 막으려면 패키지의 Warpage는 얼마로 관리되어야 하고 고객의 요구 수준은 얼마나 될까요? 15mm 이하의 크기는 1년 전만 해도 80㎛ 이내였다가, 최근에는 50㎛, 심지어 Solder가 녹는 220℃ 이상의 온도 구간에서 20㎛ 이내를 요구하기도 합니다. 앞에서 A4 용지 두께를 생각해 보시면 얼마나 변형이 적어야 하는지 아시겠지요? 이 criteria를 맞추기 위해 얼마나 고생하는지 아마 모르실 겁니다.

참고로, 30~50mm 크기의 비교적 큰 패키지는 200~250㎛ 이내를 요구합니다. 50mm 크기면 손바닥 반 만한 크기인데, 변형을 A4 종이 2장 겹친 것보다 작게 할 수 있을까요? 이것도 정말 쉽지 않답니다. 하지만 우리 앰코는 불가능을 가능으로 만들지요. 대단하지 않나요? (^^)

앗, 그럼 패키지 만병의 근원인 Warpage는 왜 발생하는 걸까요? 그리고 그것을 최소화하기 위한 방법은 무엇일까요? 다음 호에 계속 됩니다.

WRITTEN BY 손은숙

건강하고 다재다능한 명품 패키지 개발을 주업으로, 울트라 캡 잔소리꾼이지만 때로는 허당 엄마를 부업으로, 하루하루를 열심히 사는 40대 꽃중년 아줌마입니다.